## Lab 4 LMP Model -Multiplexer and Demultiplexer in Embedded System

## - Implemented by FPGAs

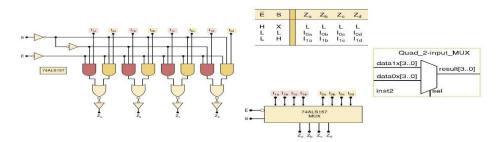

A multiplexer is a device that acts like a selector switch for digital signals. The select inputs are used to specify the input channel that is to be "connected" to the output pins. A demultiplexer works in the opposite direction by taking a digital signal as an input and distributing it to one of its outputs. The 74ALS157 contains four two-input multiplexers.

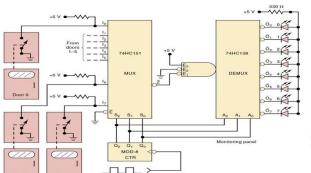

## Security monitoring system using the 74ALS138

The system shown can handle eight doors, but can be expanded to any number.

The door switches are data inputs to the MUX.

They produce a HIGH when a door is open and a LOW when it is closed.

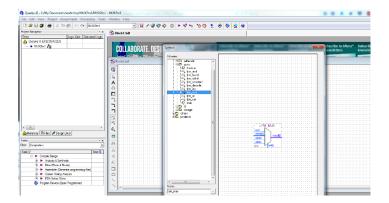

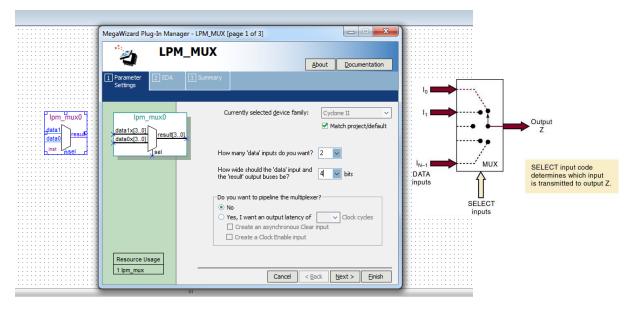

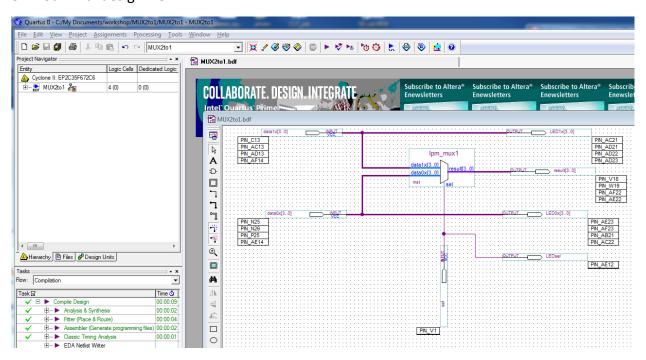

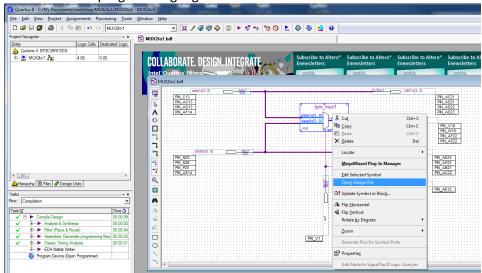

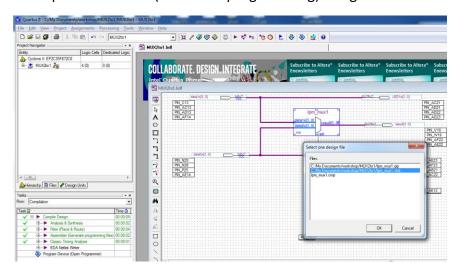

1. To ease the design process for commonly used system, such as adders, the Quartus II provide a build-in **Library of Parameterized Modules (LPM)**. For example, the *bdf* file can utilize four two-input multiplexer *lpm\_mux* module.

2. Configure *lpm\_mux* module to have VHDL as output prograaming code.

3. Configure multiplexer to select 1 of 2 inputs data source and transmit the selected data to a single output. Each of inputs has four bits.

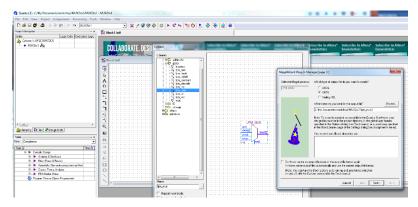

4. Click finish

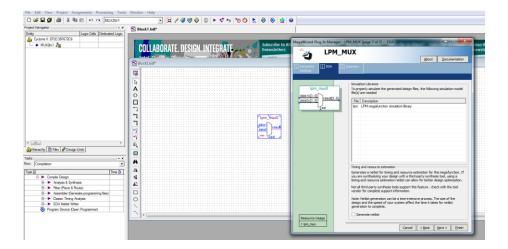

5. Click finish again

- 6. Compilation and see if any mistakes.

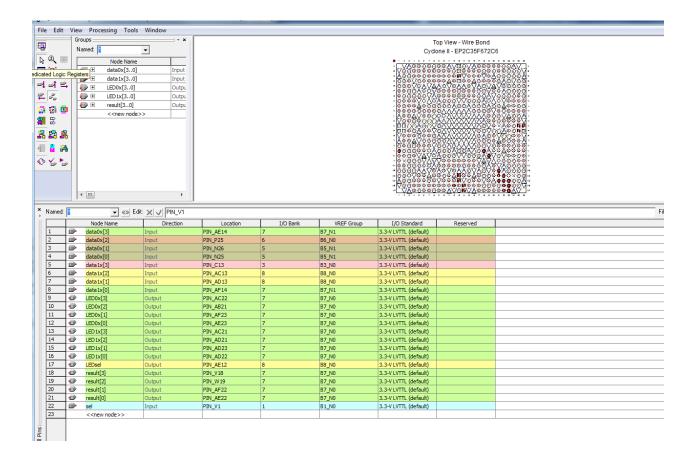

- 7. Pin planner-pin assignment

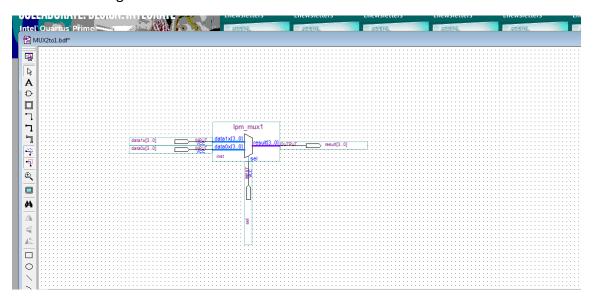

8. Your final design view

9. Compile again to include FPGA device information into your design

- 10. Download the design to FPGA IC. Observe the output LEDs and inputs Switches

- 11. Explore different led lights by your own.

- 12. Flip SW 16 to observe input (red led light)/output (green light).

If SW16 is in down position (logic 0), them output (result=data0x);

If SW16 is in up position (logic 1), them output (result=data1x);

| selector | Input group 1 (data1x)     | Input group 0 (data0x)     | Output (result)           |

|----------|----------------------------|----------------------------|---------------------------|

| SW16     | LEDR7, LEDR6, LEDR5, LEDR4 | LEDR3, LEDR2, LEDR1, LEDR0 | LEDG3, LEDG2, LEDG1,LEDG0 |

| 0 (down) | SW7,SW6,SW5,SW4            | SW3,SW2,SW1,SW0            | SW3,SW2,SW1,SW0           |

| 1 (up)   | SW7,SW6,SW5,SW4            | SW3,SW2,SW1,SW0            | SW7,SW6,SW5,SW4           |

13. View hardware program language VHDL of two-to-one MUX

14. Explore the VHDL (Hardware programming) design source code

15. VHDL source code generated

```

USE ieee.std_logic_1164.all;

LIBRARY 1pm;

USE lpm.lpm_components.all;

ENTITY lpm_mux1 IS

PORT (

: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

data0x

data1x

: IN STD_LOGIC;

: OUT STD_LOGIC_VECTOR (3 DOWNTO 0)

sel

result

END lpm_mux1;

■ ARCHITECTURE SYN OF lpm_mux1 IS

-- type STD_LOGIC_2D is array (NATURAL RANGE <>, NATURAL RANGE <>) of STD_LOGIC;

SIGNAL sub_wire0

: STD_LOGIC_VECTOR (3 DOWNTO 0);

: SID_LOGIC_VECTOR (3 DOWNTO 0);

: SID_LOGIC_VECTOR (0 DOWNTO 0);

: SID_LOGIC_VECTOR (3 DOWNTO 0);

: SID_LOGIC_VECTOR (3 DOWNTO 0, 3 DOWNTO 0);

: SID_LOGIC_VECTOR (3 DOWNTO 0);

SIGNAL sub_wire1

SIGNAL sub_wire2

SIGNAL sub_wire3

SIGNAL sub_wire4

SIGNAL sub_wire5

BEGIN

IN

sub_wire5 <= data0x(3 DOWNTO 0);

result <= sub_wire0(3 DOWNTO 0);

sub_wire1 <= sel;

sub_wire2(0) <= sub_wire1;

sub_wire3 <= data1x(3 DOWNTO 0);

sub_wire4(1, 0) <= sub_wire3(0);

sub_wire4(1, 1) <= sub_wire3(1);

sub_wire4(1, 1) <= sub_wire3(1);</pre>

lpm_mux_component : lpm_mux

GENERIC MAP (

lpm_size => 2,

=

lpm_size => 2,

lpm_type => "LPM_MUX",

lpm_width => 4,

lpm_widths => 1

sel => sub_wire2,

data => sub_wire4,

result => sub_wire0

END SYN:

```