# New York City College of Technology Computer Engineering Technology

# Designing Decoders & Programming with The Altera DE-10 Lite

Lab 004

CET 4805 Component and Subsystem Design II

Section OL40

Professor Hakan Pekcan

Spring 2021

Report Written by Maria Pedroza & Galib F. Rahman

# Table of Contents

| Objective                                   | 2 |

|---------------------------------------------|---|

| Procedure & Results                         | 3 |

| Creating A Project                          | 3 |

| Part I: Design BCD to Seven Segment Decoder | 3 |

| Conclusion                                  | 3 |

# Objective

The objective of this laboratory exercise is to use the Quartus® Prime software to virtually create a 7-segment decoder module that inputs 4 bits [D3, D2, D1, D0] and simulate said module. We will VHDL to express the design concept of a BCD to 7 Segment Decoder and create a block diagram file and waveform vector file to simulate the behavior of the module. Upon observation of the simulated results we will verify the validity of the entity's operation using the table (shown in Part I).

#### Procedure & Results

#### Creating A Project

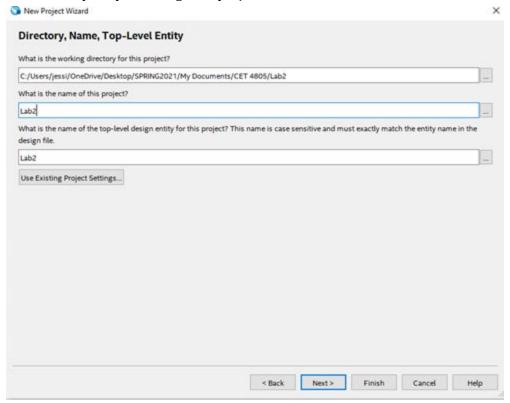

1. To begin, we will open the Quartus Software. Select **File-New Project Wizard**. Enter the appropriate drive letter for the designated storage area on the computer you are using followed by the working directory. Don't forget to create the folder **Lab2** under the subfolder of your path. Assign the project name **Lab2**.

#### Creating A VHDL File and Symbol for the Code(bdf)

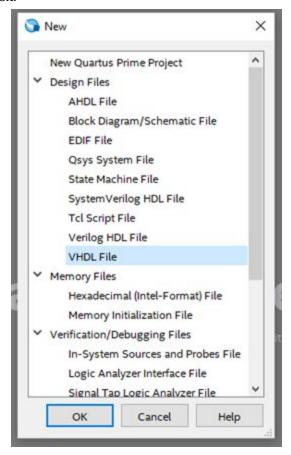

2. Open a new VDHL Device Design file (File>New) by highlighting VHDL File. Type the VHDL codes shown in Text Box.

3. File name vhdl2\_1.vhd must be chosen according to which approach is being used. Save the VHDL file as vhdl2\_1.vhd as part of our project under your subfolder. Place a check mark in the space labeled. Add file to current project and press Save.

#### DO NOT COMPILE THE FILE AT THIS POINT

4. Select **File>Create/Update>Create Symbol Files for Current File** to create a symbol file for the VHDL code entered. A display window should soon appear stating that the **Create**

**Symbol File was (or not) successful**. Click **OK** and close the Compilation Report window.

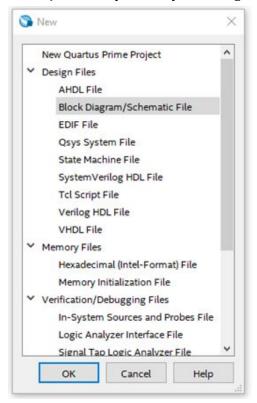

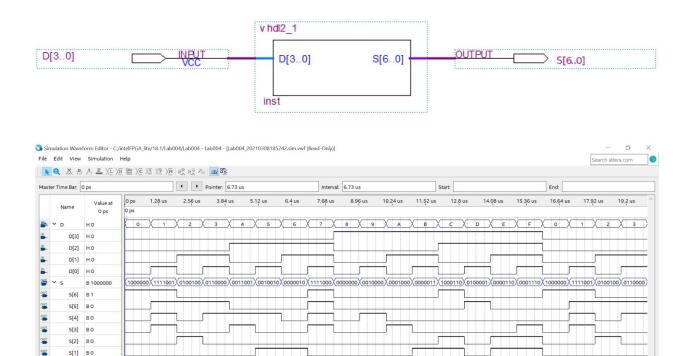

5. Open a new Schematic file (**File>New**) by highlighting **Block Diagram/Schematic File**. And click **OK**. And construct the circuit using the symbols you just create. Each symbol should be available in the Project Library in the Symbol diagonal box.

(Right click on the bdf window and then >Insert >Symbol > Project >chd2\_1)

To insert pins, right click and then >Insert >Symbol >c:/intelfpga...? >primitives > pin > input (or input)

6. Before compiling this bdf file, we need to name this bdf file and save it as a part of our project under your subfolder. Choose File > Save As and enter File name as lab2.bdf. Please a check mark in the space labeled. Add file to current project and press Save.

7. Compile the project by selecting Processing > Start Compilation, or press Ctrl-L, or use the Compilation button in the toolbar. The compilation takes several seconds. When it is complete it should give a message that indicates, "Full compilation was successful". Press OK. If unsuccessful, correct all errors and try to re-compile.

#### Simulating a Vector Waveform File (University Program vwf)

- 8. As you have done step in the Part 1, you need to create a Vector Waveform File (vwf) to simulate a design(bdf) file. Add all inputs and output, specify an end time of 20  $\mu$ s for our waveform display (Edit -> Set End Time) , and then save it as lab2.vwf.

- 9. When creating the D[3..0] bus, enter D for the bus name, select Hexadecimal for the Radix, and enter 4 for the Bus Width in the Node Properties window. When created, the D waveform will appear with a plus sign implying that it can be ungrouped to show the individual bits, D[3], D[2], D[1], and D[0].

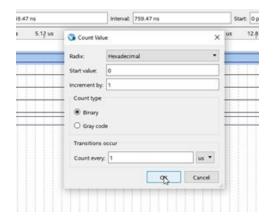

After adding the input vector D and the output vector S, highlight D and go to count Value in the simulation waveform editor toolbar as shown below.

In the Count Value window set the Radix to Hexadecimal. The start value must be 0 and increment the values by 1. This will simulate the switch inputs starting at 0000 and increment D by 1 for each clock count giving 0001 the for the next input. For count enter 1 and select us.

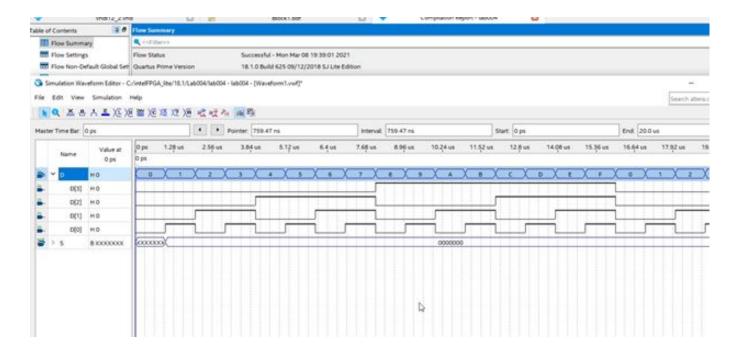

Each wave represents your input for your design, when your waveform is low, this will represent a logical 0 in your program. When the waveform is high this represents a logic 1 in your program. Together D[3] - D[0] will represent a number each count as shown below.

10. Run the simulation for your program by clicking on Run Functional Simulation in the toolbar or by going to Simulation > Run Functional simulation. The Simulation Waveform editor will give you the output for S when D = any given input. This is based on what you set it equal to in the code. In our example vhdl2\_1:

D = '0000' then S = '1000000'

D = '0001' then S = '1111001'

11. The Simulation Waveforms appear in the Simulation Report. You may have to expand the size of the Simulation Waveforms to suit your need and choose View > Fit in Window to see the entire waveform.

### Part I: Design BCD to Seven Segment Decoder

The 7 LEDs within the segment display are configured such that the anodes are tied together & connected to  $V_{cc}$ . Thus, the individual segments are activated once a logic value of 0 is applied. The table below demonstrates the 4-bit inputs (D[3..0])and corresponding outputs of the module (S[6..0]).

| Symbol | D3 | D2 | D1 | Do | Shape | S6<br>(g) | S5<br>(f) | S4<br>(e) | S3<br>(d) | S2<br>(c) | S1<br>(b) | So<br>(a) |

|--------|----|----|----|----|-------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|

| 0      | 0  | 0  | 0  | 0  |       | 1         | 0         | 0         | 0         | 0         | 0         | 0         |

| 1      | 0  | 0  | 0  | 1  |       | 1         | 1         | 1         | 1         | 0         | 0         | 1         |

| 2      | 0  | 0  | 1  | 0  | 2     | 0         | 1         | 0         | 0         | 1         | 0         | 0         |

| 3      | 0  | 0  | 1  | 1  |       | 0         | 1         | 1         | 0         | 0         | 0         | 0         |

| 4      | 0  | 1  | 0  | 0  |       | 0         | 0         | 1         | 1         | 0         | 0         | 1         |

| 5      | 0  | 1  | 0  | 1  | 6     | 0         | 0         | 1         | 0         | 0         | 1         | 0         |

| 6      | 0  | 1  | 1  | 0  | 6     | 0         | 0         | 0         | 0         | 0         | 1         | 0         |

| 7      | 0  | 1  | 1  | 1  |       | 1         | 1         | 1         | 1         | 0         | 0         | 0         |

| 8      | 1  | 0  | 0  | 0  | В     | 0         | 0         | 0         | 0         | 0         | 0         | 0         |

| 9      | 1  | 0  | 0  | 1  |       | 0         | 0         | 1         | 0         | 0         | 0         | 0         |

| А      | 1  | 0  | 1  | 0  | В     | 0         | 0         | 0         | 1         | 0         | 0         | 0         |

| В      | 1  | 0  | 1  | 1  | 8     | 0         | 0         | 0         | 0         | 0         | 1         | 1         |

| С | 1 | 1 | 0 | 0 | 1 | 0 | 0 | 0 | 1 | 1 | 0 |

|---|---|---|---|---|---|---|---|---|---|---|---|

| D | 1 | 1 | 0 | 1 | 0 | 1 | 0 | 0 | 0 | 0 | 1 |

| Е | 1 | 1 | 1 | 0 | 0 | 0 | 0 | 0 | 1 | 1 | 0 |

| F | 1 | 1 | 1 | 1 | 0 | 0 | 0 | 1 | 1 | 1 | 0 |

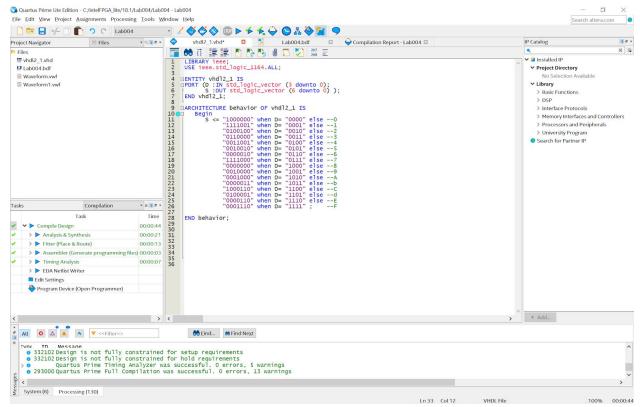

VHDL Code

For this portion of the exercise we utilized when/else with the conditional concurrent signal assignment statement to describe the behavior of the designed entity *vhdl12\_1*. When one or more of the signals change value (on the right hand side), the statement is executed and evaluates the conditions from top to bottom, if true the corresponding expression is executed and the value is assigned to the given signal.

VHDL Code

# Conclusion

S[0]

Upon completion of this laboratory exercise, we have successfully utilized the Quartus® Prime software to create & simulate a 4-bit input 7 segment (common anode) decoder module. We have used VHDL to define the behavior of our circuit and designed a block diagram to represent the decoder as an entity by assigning the appropriate bus values for both input and output. Upon successful compilation of both the VHDL and block diagram we created a Waveform Vector File to observe the results.